前不久,“第一个常温常压超导体”的论文在全球掀起超导科技话题热潮,超导带来的科技变革可能带来的颠覆性让全球科技爱好者开启无限科幻畅想——

#对电的利用率达到百分百,不再有损耗之忧;

#输电没有电阻,远距离传输也就不再需要高压电;

#所有发电机和电路系统全部更新换代;

#高能加速器、容量更大的超级计算机更容易实现;

#医院里面用的核磁成像装置就将不需要用任何低温制冷液体,使用价格非常便宜,更大程度地惠及人类;

#室温超导体可以全面提升磁悬浮列车的安全性,会有成本更低、安全性能更高的磁悬浮列车投入运营……

一言以蔽之,室温超导真正实现后,整个世界将会发生翻天覆地的变化!

可惜,科技变革未能实现,倒是引起全球证伪的实验热潮。

业界普遍认为超导的实现的路程可能依然漫长,然而在追求低导通电阻带来的技术变革上,其实有很多领域依然有探索的价值,并不断实现突破,带来新的技术升级。功率器件SiC FET的导通电阻RDS(on)便是其中之一。

作为全球功率器件技术的重要开发者,Qorvo在相关的技术探索中一直走在前列。

2019年12月,7mΩ、650V新型SiC FET发布。7mΩ的低RDS(on)特性是当时业界最低值,从而使得在逆变器设计中可以实现超过99%的效率,高效率的实现也得益于其出色的反向恢复性能以及在续流模式下的低导通压降。适用于电动汽车(EV)逆变器、高功率DC/DC转换器、大电流电池充电器和固态断路器等高功率应用。

2020年2月,DFN 8×8小尺寸封装下、业界最低34mΩ的SiC FET发布。通常情况下,要达到较低的RDS(on),就需要增大FET的尺寸;因此,在紧凑的封装尺寸下获得较低的RDS(on)更具有挑战性。650V SiC FET的UF3SC065030D8S采用DFN 8x8封装,其RDS(on)为34mΩ,该产品在该电压等级中具有最低的RDS(on)。

2021年9月,6mΩ、750V的TO-247-4L封装系列SiC FET发布。该系列SiC FET器件最低RDS(on)为6mΩ,比业界同类产品的最低RDS(on)还低一半。该系列器件还能提供5uS的短路承受能力。

2022年7月,采用表贴D2PAK-7L 封装的750V 9mΩ SiC FET发布。这种封装热阻小,能满足需要高效率、低导通损耗的高功率应用的电源方案,适合快速增长的车载充电器、软开关DC/DC转换器、电池充电和IT/服务器电源等对效率要求高的应用场景。

2023年3月,采用 TOLL 封装的 5.4 mΩ 750V SiC FET发布。这是750V SiC FET系列中首款采用TOLL封装的产品。这些器件热阻进一步减低、尺寸进一步紧凑化,适用于多种空间受限应用,例如功率在几百瓦至几千瓦的AC/DC电源、固态继电器,以及电流高达100A及以上的固态断路器。特别是工业应用,尤其那些需要可兼具灵活性和尺寸紧凑、高效率及高可靠性的大功率电源设计。

“遥遥领先”背后,看看降低每0.1mΩ的硬核技术在所有非超导介质中传递会产生能量损耗一样,在所有SiC FET器件中电流传导都会产生一定的功率损耗。SiC FET器件传导中的功率损耗与其额定RDS(on)值成正比,这种损耗等效于系统效率的下降,更低的RDS(on)意味着更高的效率。

然而,要达到较低的RDS(on)并非易事——需要增大FET的尺寸。而增大尺寸便意味着增加了成本——显然,器件厂家必须要在成本、尺寸和RDS(on)之间平衡。诚如上面的一众低于10mΩ的产品中,650V SiC FET的UF3SC065030D8S采用DFN 8x8封装,其34mΩ的RDS(on)同样在该电压等级中具有最低的RDS(on),主要是因为Qorvo的SiC FET技术与传统封装相比,相同的阻抗情况下,芯片尺寸远比其他竞争者的芯片尺寸小,因此Qorvo的SiC FET产品可以完美契合DFN 8x8封装对芯片尺寸的需求,优化了体积和空间占比,封装厚度<1mm,在尺寸和RDS(on)上进行平衡实现目标性能的最优化。

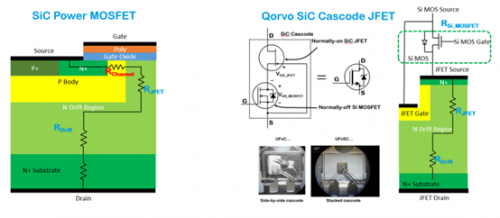

就Qorvo的SiC FET而言,由于芯片整体尺寸远远小于竞争对手SiC、硅等功率技术产品,应用灵活性远高于同类产品。这背后,多款器件得益于Qorvo开发出的独特共源共栅结构的SiC技术,该技术将SiC JFET和Si MOSFET封装在一起,让器件能够充分发挥其宽带隙开关技术和更简单的Silicon MOSFET栅极驱动带来的所有能效优势。

Qorvo的每一代芯片都变得越来越小,但应用的功率等级并不会降低甚至更高。为了解决热问题,碳化硅芯片变薄,随着芯片变薄,芯片的寄生参数随之而降低,带来的好处是开关速度变快,相应的Junction-case的热阻也降低了。然而,由于薄晶片容易断裂,因此处理起来极为困难。在这里,需要解决大量的工程问题,例如其中也涉及到的烧结技术至关重要,也显著降低了RDS(on)。

追求极限低的“超导”RDS(on),越来越多的应用正在受益

通过优化开关损耗和减小RDS(on)从而减小导通损耗已经在越来越多的项目中得到验证,从而使客户和厂家广泛受益。例如电动车辆中能实现更强大的新应用,如牵引驱动、车载和非车载充电器,以及可再生能源逆变器、功率因数校正、电信电源转换器和AC/DC或DC/DC功率转换的所有功率级。

Qorvo的碳化硅器件兼而有之这两个优势,能将诸如太阳能逆变器和储能等可再生能源设备的散热量限制在最低限度。通过采用SiC FET取代IGBT在牵引逆变器的应用可以提高开关频率,减少有色金属的使用和电感及电容的数值,驱动电流波形更理想,并可以节省更多功耗,从而在200kW输出时将半导体效率提高1.6%,达到99.36%,功率损耗降低3kW。

本文转载自Qorvo半导体微信公众号