1、引言

近年来,随着无线通信技术的迅速发展,对全集成、高性能、低成本的无线收发机的需求变得越来越迫切。而发射机系统中的一个关键模块就是功率放大器,从功耗方面考虑,功率放大器的功率损耗在发射机的总功耗中占有很大比例。于是一个高效率的CMOS 功率放大器的设计就显得尤为重要。而随着RF CMOS技术的不断发展 ,使得基于Si CMOS工艺的射频集成电路在GHz频段上的性能上有了很大的提高,而且它具有高集成度、低功耗、低成本的特点,能够和基带数字电路相兼容。最终可以实现片上系统集成(SOC)。所以近年来对于Si的CMOS射频集成电路的研究成为国际上研究的热点。

功率放大器通常分为线性和非线性两大类,线性放大器有四种: A、B 、AB和 C,它们的主要差别在于栅极偏置情况不同,这类传统的功率放大器具有较高的线性度,但效率较低;非线性放大器主要有D、E和F。对于本文的无线局域网而言,由于要求具备高线性。所以两级分别采用的是A和AB类放大模式。

2、功率放大器的电路设计

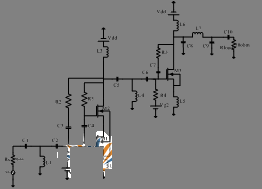

一个典型的功率放大器一般包括输入匹配网络、晶体管放大电路、级间匹配网络、偏置网络和输出阻抗匹配网络等 ,如下图1所示。

2.1 自偏置共源共栅(Cascode)结构

对于功放而言,标准的0.18um CMOS工艺的晶体管漏栅间的最大电源电压为2V,击穿电压大约是4V。在功放中,管子漏端的直流与交流电压之和可达到2-3倍的电源电压,这就给管子的栅氧化层带来击穿的危险。在设计PA时,晶体管所能承受的最高电压Vmax受到晶体管击穿电压的限制,而最小电压则受到Knee电压的限制。而功率放大器采用Cascode结构可以缓解晶体管击穿的压力,提高功率放大器输出电压的摆幅,从而降低对晶体管最大电流能力的要求,提高功率放大器的效率,并减小输出晶体管的尺寸。实际在共源共栅结构的放大器中,共栅晶体管是电压击穿和热载流子效应的瓶颈。

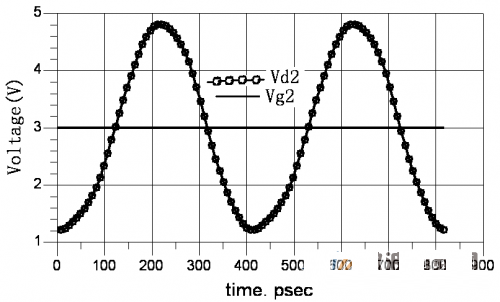

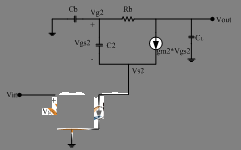

所以本文采用了Cascode自偏置结构和厚栅器件,不仅可以改善深亚微米CMOS器件的低击穿电压,同时还可以减小热载流子效应影响。图3所示的传统Cascode放大器中M2的栅漏电压波形,Vg2一直固定在3V,Vd2的正峰值电压在4.8V,所以栅漏电压差为1.8V。为了克服这个问题,图4所示为自偏置Cascode结构放大电路,该结构把M2管的漏端交流电压Vd2引入到栅端Vg2上,使我们在设计功放时两个MOS管尽可能有相同的最大漏栅电压。所以,在热载流子效应出现之前M2管有一个大的信号摆幅。对G2的偏置是通过Rb-Cb来实现的。图6所示为M2管的Vd2对Vg2的电压波形,其最大电压差为1.4V。与传统电路比较降低了0.4V,所以自偏置的M2管的Vdg的电压差相对传统结构的M2管降低了23%。

图2 传统的Cascode放大器

图3 传统的Cascode放大器中M2的栅漏电压波形 图4 自偏置Cascode放大器

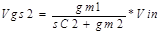

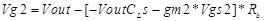

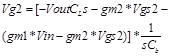

图5 自偏置Cascode放大器的等效电路图 根据上面的等效电路图,我们能够得到两个

的表达式: 的表达式:

(1) (1)

(2) (2)

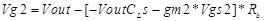

同理,我们也可以得到两个

的表达式: 的表达式:

(3) (3)

(4) (4)

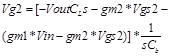

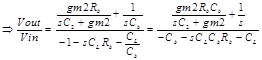

把(2)式代入式(3)和式(4),并令它们相等可得下面的增益表达式:

(5) (5)

(6) (6)

(7) (7)

(8) (8)

从(8)式的增益表达式可知,如果Rb或cb增加,放大器的增益都会有所增加,但是通过电路仿真后的电压波形可知,若Rb或cb增加,导致Vg2的电压摆幅的降低,从而漏端节点电压波形将会在输入功率较低的情况下就开始失真。所以Rb或cb的值不仅要依据M1和M2管尽可能有相同的栅漏信号摆幅,同时也力求在增益和线性之间有个较好的折中来确定。

图6 自偏置Cascode放大器中M2的栅漏电压波形 2.2、功率放大器的设计与仿真

对于本文的无线局域网应用而言,由于采用的是非恒包络调制,要求具备高线性,所以本功率放大器第一级工作在A类,第二级工作在AB类。A类放大模式能提供更好的线性度,而AB类放大模式比A类放大模式又具备更高的效率。所以,本文的功放在线性度和效率之间进行了较好的折中。

2.2.1、放大电路设计

为了达到功放的设计要求,由于高频下单级放大器不能实现预定的功率增益指标,所以采用两级放大结构。如图7所示,第一级采用共源共栅结构,在提供合适的电压增益的同时 ,提高了前后级电路的隔离度,为阻抗匹配提供了便利条件。第二级采用的是厚栅的共源结构以承受更高的电源电压。主体分为以下几个部分:(1) C1、C2、L1为输入阻抗匹配,片内实现,使电路的输入端与50Ω端口匹配。

L3为第一级放大电路的扼流电感,考虑到功放中流过的电流很大,片外实现。(2) M1与M2为驱动级。(3) C5、C6、L4为级间匹配网络,除了两级之间匹配外,还可以用于调整放大电路的增益平坦度[5]。(4) M3为功率级。(5) C8、C9、L7构成∏型输出匹配网络,能够有效抑制偶次谐波分量,实现最佳负载匹配[6]。为了减少损耗,输出匹配网络C8、C9、L7和扼流电感L6也采用片外实现。(6) CMOS的接地电感对放大器的增益和效率有很大影响,所以在电路仿真时把键合线和pad的寄生效应一起考虑了。其中L2和L5为多PAD的键合线电感。

图7 功率放大器电路图 2.2.2、仿真结果

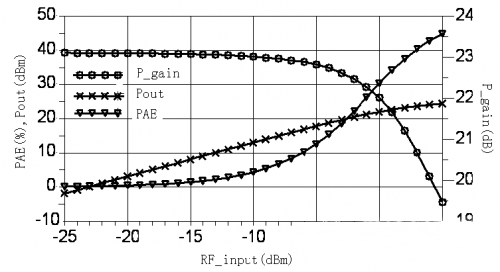

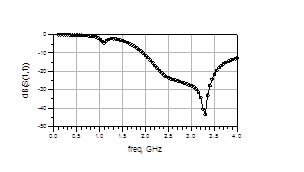

电路的性能仿真和优化是利用Agilent 公司的ADS(Advanced Design System)软件完成的。放大器中的晶体管工作在大信号状态,非线性效应非常显著,因此设计放大器电路时,小信号电路的等效模型不再适用,必须充分考虑晶体管的非线性特性。图8为仿真得到的输出功率、增益和PAE随输入功率的变化曲线。由图可知,在输入功率小于0dBm的信号范围内,该功放的增益有22dB。在1dB功率增益压缩点处输出功率为22dBm,相应的PAE为30.4%。图9为功放的S11参数随频率的变化曲线图,由图可知,S11在中心频率2.45GHz附近都小于-20dB所以输入匹配基本达到设计要求。

图8 输出功率、增益和PAE随输入功率的变化曲线 另外,仿真所得到的其它重要参数有:输出三阶交接点约为29 dBm;稳定因子K在工作频段内有K>1。

图9 功放的S11参数曲线 2.2.3、版图设计

版图设计采用了 Cadence软件。功率放大器采用 SMIC 0.18μm CMOS工艺。其中放大电路中使用的晶体管采用射频模型。本版图设计主要考虑了以下几个方面的问题:

(1)由于功放中流过的电流很大,所以在电源线和地线采用几层金属并联的方式来避免发生电迁移。(2)接地键合线的寄生电感严重影响各级电路的功率输出。所以,为了使接地键合线寄生电感尽量小,设置多个对地焊盘并引出多条键合线到地线上。(3)对于高频信号线 ,尽量采用顶层和上层金属 ,且最好遵循最短信号线的原则用于减少寄生电容、耦合等因素引起的损耗。

图10 PA版图 3、结论

采用SMIC 0.18um CMOS 工艺RF模型设计了工作于2.45GHz WLAN的功率放大器。通过自偏置技术的应用,该功放工作在3V电源电压下,其仿真性能指标表明最大输出功率可达24.5dBm,对应的PAE达到40%,功率增益为23dB,适合无线局域网802.11b的系统应用。

|  /2

/2