以下文章来源于Qorvo Power ,作者UnitedSiC现Qorvo

您如何在提高开关速度和增加设计复杂度之间寻求平衡?本博客文章将讨论此类权衡考量,并提供了一种更高效的方法,有助于您克服设计挑战并充分发挥 SiC 器件潜力。

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

随着人们对高效率、高功率密度和系统简单性的需求不断增长,碳化硅 (SiC) FET 因其较快的开关速度、较低的 RDS(on) 和较高的额定电压,逐渐成为对电力工程师极具吸引力的选择。

但是,SiC 器件较快的开关速度会导致更高的 VDS 尖峰和更长的振铃持续时间,从而在高电流电平下引入了更多的 EMI。对于从事电动汽车和可再生能源等高功率应用的工程师来说,如何在提高效率并充分发挥先进技术潜力的同时,避免过于复杂的设计将会是一大难题。

什么是 VDS 尖峰和振铃?

寄生电感是导致 VDS 尖峰和振铃的根本原因。从 SiC MOSFET 的典型关断波形(图 1)可以看出,栅极-源极电压 (VGS) 在 18V 至 0V 之间,关断的漏极电流 (ID) 为 50A,且总线电压 (VDS) 为 800V。由于 SiC MOSFET 具有更快的开关速度,所以会出现较高的 VDS 尖峰和较长的振铃持续时间。较高的 VDS 尖峰会减少器件应对闪电和负载突变等条件导致的电压问题的裕量。较长的振铃持续时间也会引入更多的 EMI。这种现象在高电流电平下更加明显。

图 1:SiC 器件的较快开关速度所导致的关断 VDS 尖峰和振铃

传统方法

抑制EMI 的常规解决方案就是使用高栅极电阻 (RG) 来降低电流变化率 (dI/dt)。但实际上,使用高 RG 会显著增加开关损耗,进而损失效率,所以在使用这种方法时,我们不得不在效率和 EMI 之间做出取舍。

另一种解决方案是减少电源回路中的杂散电感。但是,这需要重新设计PCB 布局,并需要使用尺寸更小、电感更低的封装。此外,PCB 上能够减小的电源回路面积是有限的,而且也需要遵守相关安全法规规定的最小间距和最小间隙。此外,更小巧的封装还会导致热性能降低。

我们还需要考虑滤波器,以帮助我们满足EMI 要求并简化系统权衡。除此之外,我们还可以使用控制方法来减少 EMI。例如,频率抖动技术可通过扩展电源的噪声频谱范围来减少 EMI。

新方法

一个简单的 RC 缓冲电路可以帮助克服设计挑战并充分发挥 SiC 器件的潜力,是一种更为高效的解决方案。事实证明,这个简单的解决方案可以在广泛的负载范围内更高效地控制 VDS 尖峰并缩短振铃持续时间,并实现可以忽略的关断延迟。

得益于更快速的 dv/dt 和额外的 Cs,缓冲电路还具有更高的位移电流,从而可以减少关断过渡期间的 ID 和 VDS 重叠。

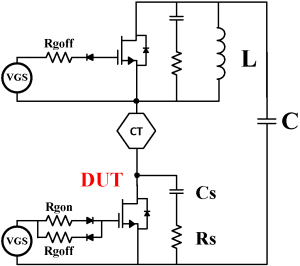

可以通过双脉冲测试 (DPT) 来证明缓冲电路的有效性。该测试采用了带感性负载的半桥配置。高端和低端都使用相同的器件,VGS、VDS 和 ID 均从低端器件测量(图 2)。

图 2:半桥配置(顶部和底部使用相同的器件)

使用电流互感器 (CT) 测量器件和缓冲电路的电流。因此,测得的开关损耗包括器件开关损耗和缓冲电路损耗。

其中的缓冲电路由 SiC MOSFET 漏极和源极之间的一个 10Ω 电阻和一个 200pF 电容串联组成。

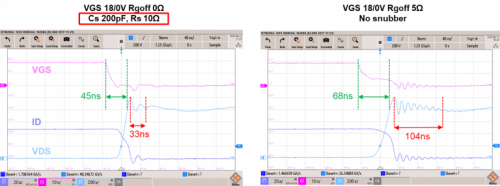

图 3:RC 缓冲电路可更有效地控制关断 EMI

首先,我们比较关断时的情况(图3)。测试的设备对象与图 1 相同。左侧波形使用 RC 缓冲电路和低 RG(off),而右侧波形则使用高 RG(off),未使用缓冲电路。这两种方法都可以限制关断 VDS 峰值电压。但是,使用缓冲电路之后,只需 33ns 即可抑制振铃,而高 RG(off) 的振铃持续时间仍超过 100ns。与使用高 RG(off) 相比,使用缓冲电路时的延迟时间更短。由此可判断,缓冲电路有助于在关断时更有效地控制 VDS 关断尖峰和振铃持续时间。

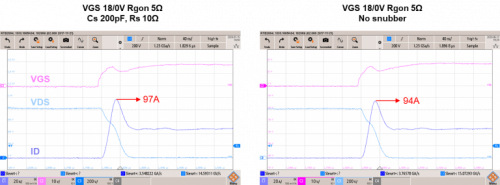

图 4:RC 缓冲电路在导通期间的有效性

在导通时(图4),将使用 RC 缓冲电路和 5Ω RG(on) 的波形与未使用缓冲电路的波形进行比较可以发现,使用缓冲电路时,反向恢复电流峰值 (Irr) 略有提高,从 94A 提高到了 97A,除此之外,其对导通波形的影响可以忽略不计。

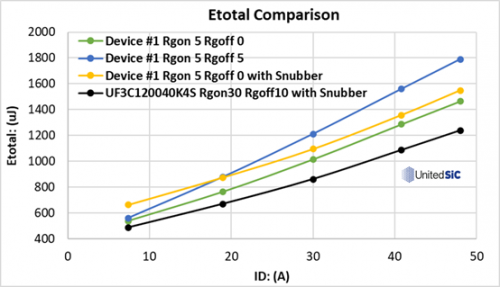

这表明,与高 RG(off) 相比,缓冲电路有助于更有效地控制 VDS 尖峰和振铃持续时间。但缓冲电路能否更高效呢?(图 5)

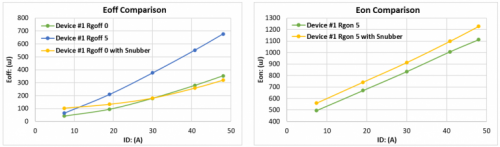

图 5:比较缓冲电路与高 RG(off) 之间的开关损耗(Eoff、Eon)

在 48A 时,高 RG(off) 的关断开关损耗是使用缓冲电路和低 RG(off) 时的两倍以上。由此证明,缓冲电路在关断时更高效。因为缓冲电路可实现更快速的开关,同时还可以更好地控制 VDS 尖峰和振铃。

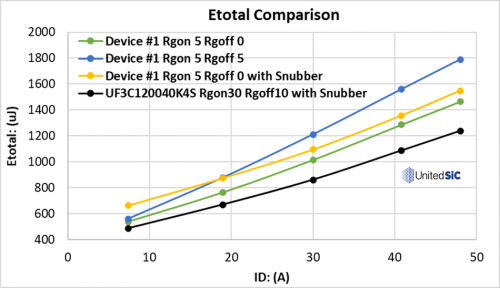

从导通开关损耗的角度看,使用缓冲电路时,Eon 平均增加了 70µJ。为了充分估计整体效率,我们需要将 Eoff 和 Eon 相加,然后比较 Etotal(图 6)。在全速开关器件时,可以很明显地看出缓冲电路在漏级电流为 18A 以上时效率更高。对于在 40A/40kHz 下开关的 40mΩ 器件,在使用高 RG(off) 与使用低 RG(off) 和缓冲电路之间,每个器件的开关损耗差为 11W。

图 6:比较缓冲电路与高 RG(off) 之间的开关损耗 (Etotal)

因此我们可以推断,与使用高 RG(off) 相比,使用缓冲电路是一种更高效的解决方案。

随着第 4 代 SiC 器件进入市场,这种简单的设计解决方案将继续提供更低的总开关损耗,继续帮助优化系统功率效率。

关于简单的缓冲电路如何在 UnitedSiC SiC 器件中实现出色效率的更多信息,请观看我们近期的研讨会:尽可能地降低 SiC FET 的电磁干扰和开关损耗。

本文转载自Qorvo半导体微信公众号