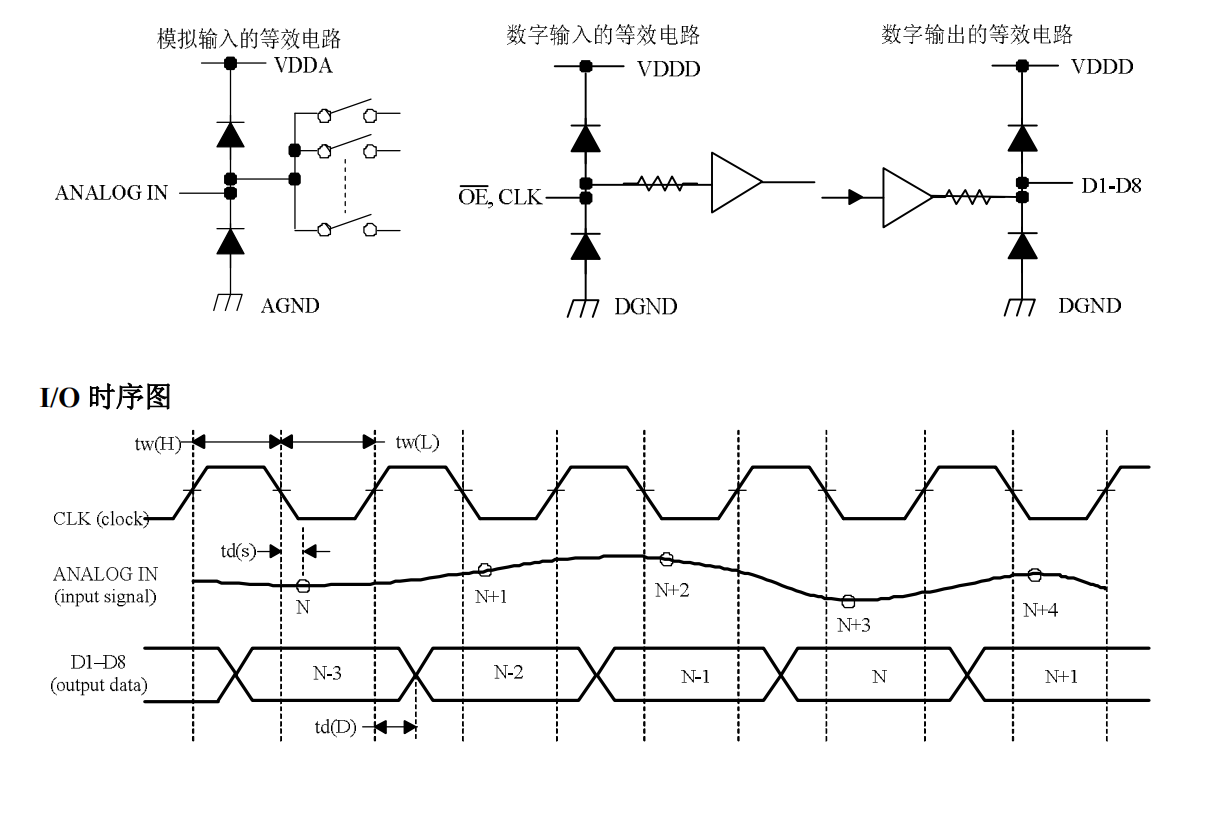

输入/输出结构示意图

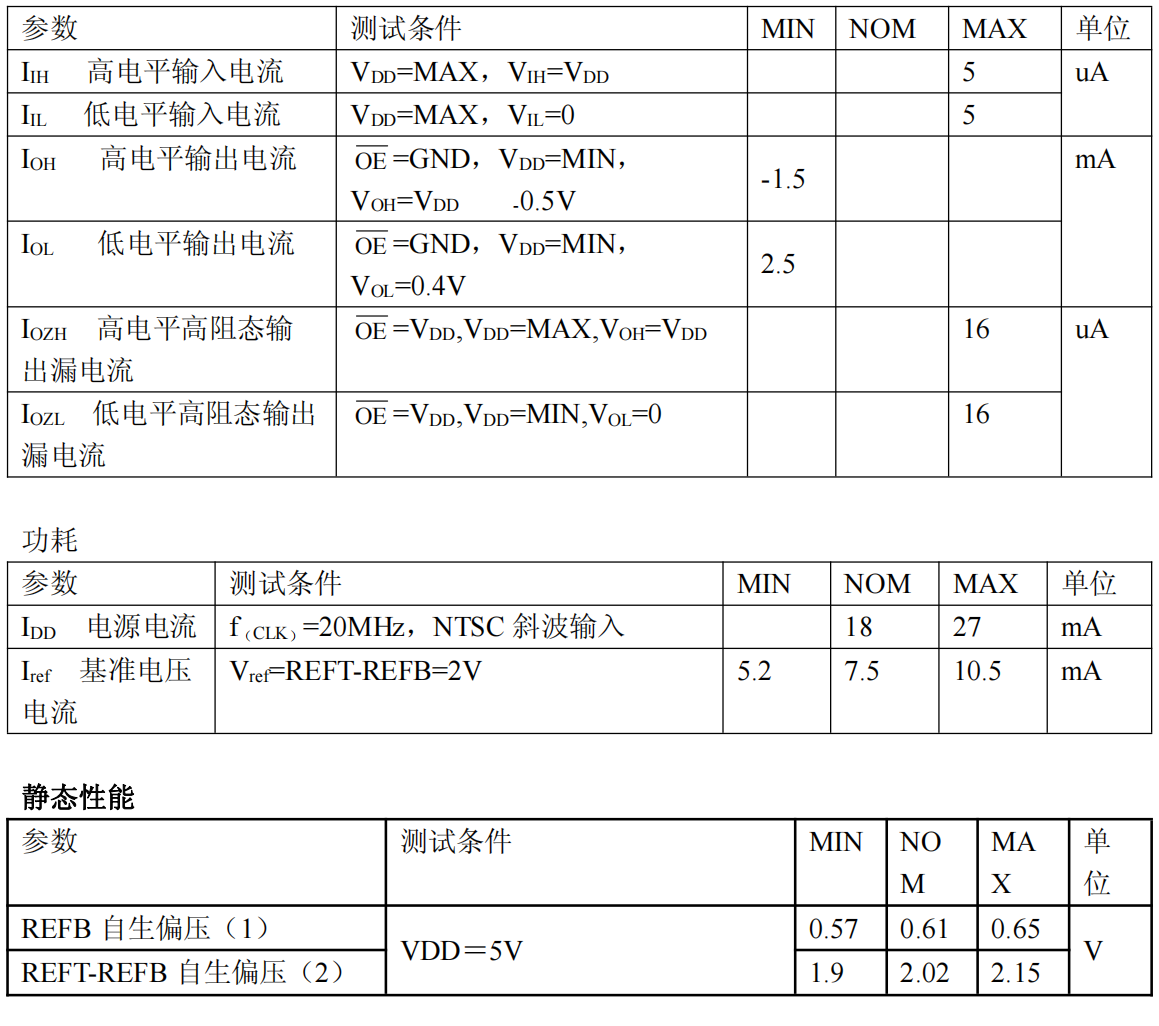

电学特性

VDD=5V,VREFT=2.5V,VREFB=0.5V,f(CLK)=20MHz,TA=25ºC 时的电学特性(除特别说明外)

数字 I/O

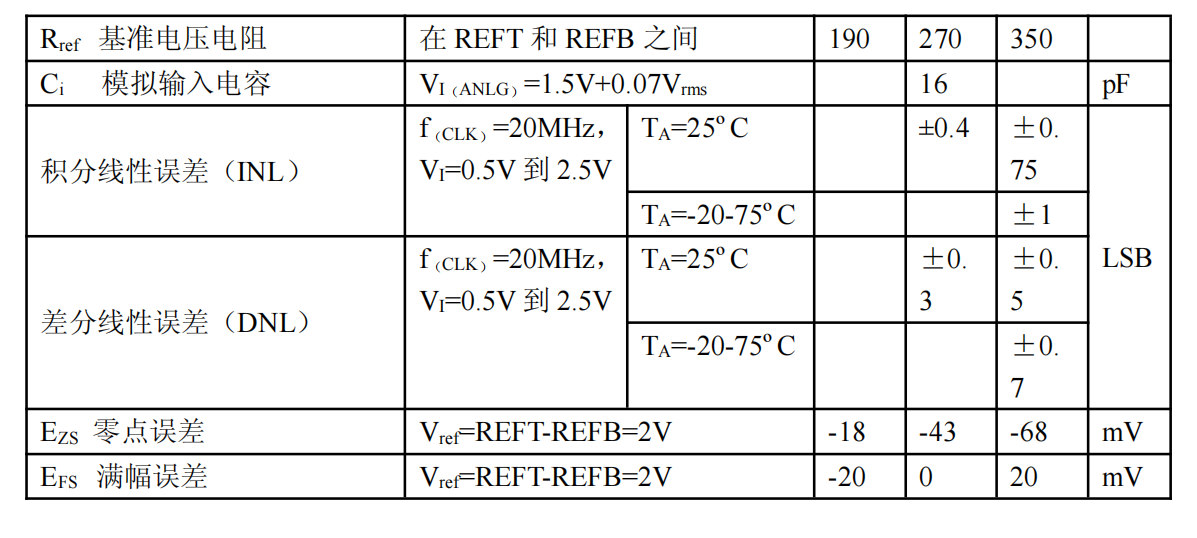

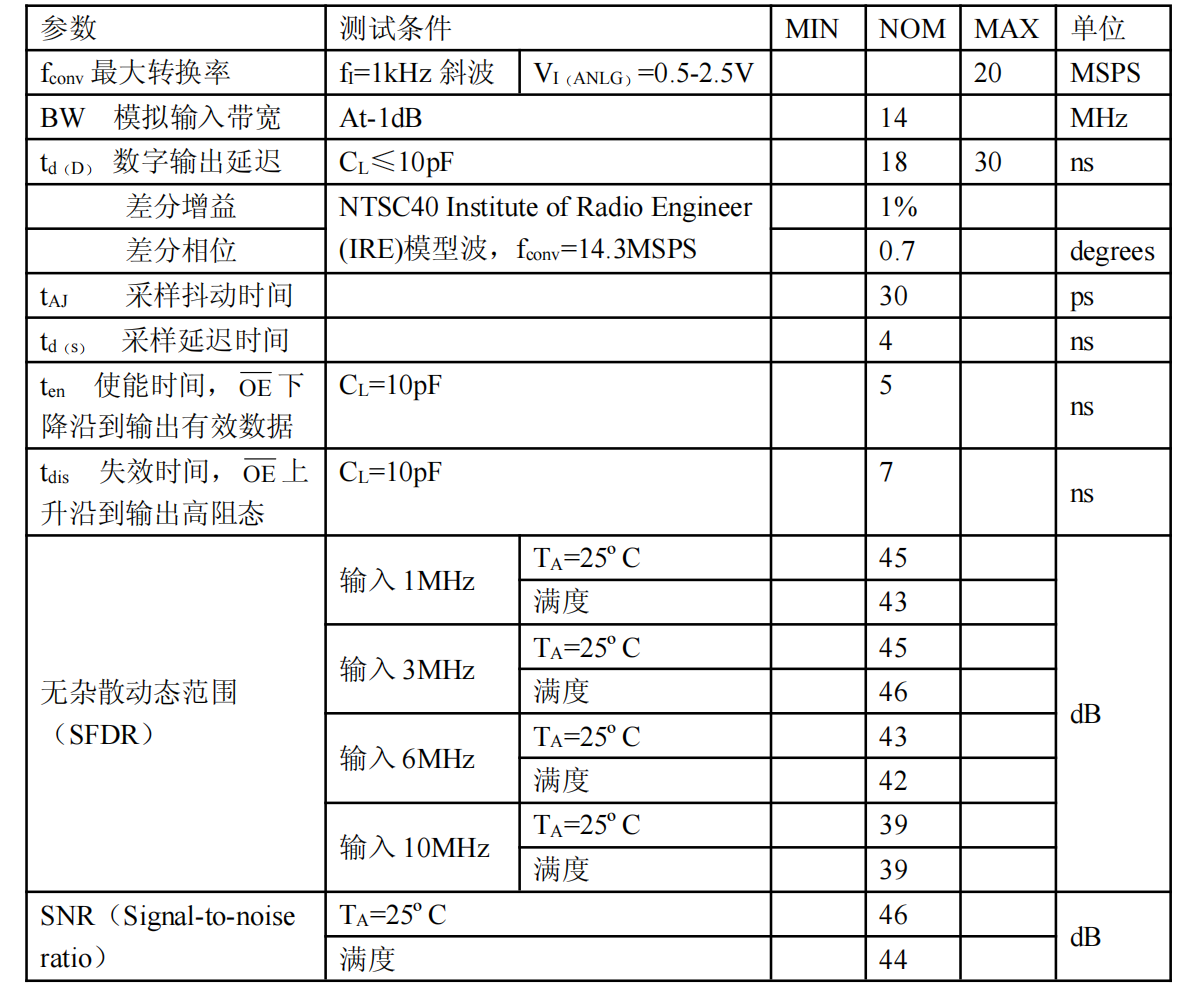

工作特性

工作条件 VDD=5V,VREFT=2.5V,VREFB=0.5V,f(CLK)=20MHz,TA=25ºC 时(除非特别说明

外)

功能说明

MS2510 是具有两个低位比较器块的半闪速(semiflash)ADC(每四位一个比较器)。如图 3 所示,输入电压 VI(1)在 CLK1 的下降沿采样入高位比较器块和低位比较器块(A),S(I)。高位比较器块在 CLK2 上升沿确定高位数据 UD(1),同时,低基准电压(lower referencevoltage)产生与高位数据相对应的电压 RV(1)。低位比较器块(A)在 CLK3 上升沿确定低位数据 LD(1)。VD(1)和 LD(1)在 CLK4 的上升沿组合在一起并输出为 OUT(1)。根据上面所述的内部操作,输出数据滞后模拟输入电压采样点 2.5 个时钟。输入电压 VI(2)在 CLK2 下降沿被采样,UD(2)在 CLK3 的上升沿最后确定,LD(2)在 CLK4 的上升沿被低位比较器块(B)最后确定。OUT(2)在 CLK5 上升沿输出。

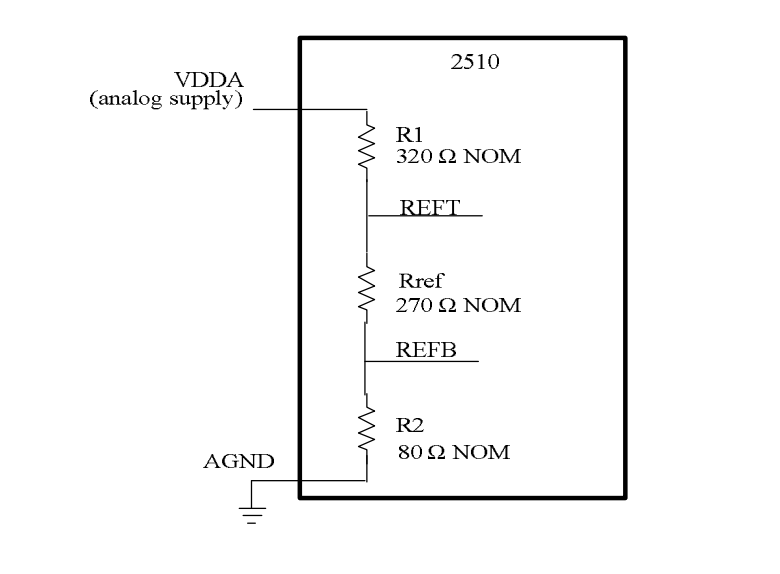

内部基准

工作模式

MS2510 具有三个内部电阻以便能产生内部基准电压。这些电阻连接到 VDDA,REFT,REFB 以及 AGND。

内部产生的基准电压,如图 4 所示那样连接。这种连接提供用于额定数字输出的标准视频 2V 基准。

强度超出所列的极限参数可能导致器件的永久性损坏,这些仅是极限参数,并不意味着

在极限参数条件下或在任何其他超出推荐工作条件下所示参数的情况下器件能有效地

工作。 延长在极限参数条件下的工作时间会影响器件的可靠性。

应用资料

以下注记是应当与 MS2510 一起使用的设计推荐项。

为了减少系统噪声,外部模拟和数字电路应当实际上分离开来并尽可能屏蔽。

MS2510 的 PIN9(VDDD)与 PIN11(VDDA)的供电,请串入 100 欧姆电阻隔离。

在整个评估和生产过程中应当使用射频 (RF)试验板或印制电路板 (PCB)技术。 用于测试评估(bench evaluation)的试验板应当镀铜。

因为 AGND 和 DGND 在内部未连接,所以这些引脚需要在外部连接。采用试验板时,这些地线应当通过具有良好电源旁路的单独引线连接。为了使拾取的噪声为最小,最好把隔开的双铰线电缆(separate twisted-pair cabels)用于电源线。在印制电路板布局上应用使用模拟和数字地平面。

VDD 至 AGND 和 VDDD 至 DGND 应当分别用 1μF 电容器去耦,去耦电容应当尽可能靠近它所影响的器件引脚处。对 0.01μF 电容,推荐使用陶瓷芯片电容器。对模拟和数字地,为了确保无固态噪声(solid noise-free)的接地连接,试验时应当小心。

VDD,AGND 以及 ANALOG IN 引脚应当与高频引脚 CLK 和 D0-D7 隔离开来。当可能时,在印制电路板上 AGND 走线应当放在 ANALOG IN 走线的两侧以供屏蔽之用。

在测试与使用器件时,在感兴趣的频率范围内连接到模拟输入端的驱动源电阻应当 是10Ω或更小的数值。

/2

/2