本文将带您深入探讨设计工程师在热设计过程中需要关注的一些关键问题。具体来说,我们将聚焦大功率氮化镓(GaN)器件及其在实际应用中所面临的相关热问题。

针对可靠性的热设计

热设计是一个复杂的课题,但其中也有一些基础原理值得深入探讨。首先让我们回顾一下在印刷电路板(PCB)上采用塑封半导体时的一些基本知识。

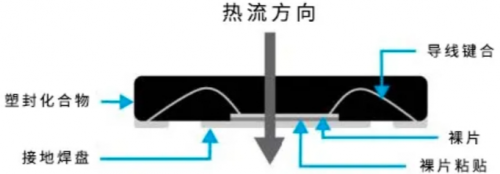

热设计过程中,热路径的规划是首先要考虑的因素;它为半导体产生的热量提供了一条通向外界环境空气的路径。这条热路径一般会通过接地焊盘穿过器件封装的底部(如图1所示)。因此在应用设计中,应当选择那些能够通过器件接地片将热量从封装底部有效引出的PCB。

图1,图中所示的顶部塑封元件展示了热量

如何从裸片顶部向下流经封装接地焊盘的过程

在此类封装中,由于塑封化合物导热性能不佳,试图从封装顶部吸取热量的方法并不奏效;而从顶部冷却又可能导致结点和沟道温度过高,从而引发器件性能下降甚至失效。

为确保采用正确的排热方法,在设计系统或最终产品时,尽可能多地利用半导体供应商提供的信息和材料(包括S2P参数和PCB Gerber文件等)非常重要。例如,导通孔的放置和创建对于从设备中排出热量并提高部件可靠性十分关键——这些类型的说明和导通孔的放置,通常可在半导体供应商提供的PCB Gerber文件中找到。

接地片与PCB之间的焊接附着物,应选用能够高效优化散热的高品质材料。通孔的位置、大小和样式往往由供应商根据性能优化原则提供,因此应在供应商的指导下使用。通孔的位置、样式和类型对于实现低热阻的散热通道具有重要作用。使用散热片时,最好将其连接至IC结点或沟道的最低阻抗路径上。

此外,PCB的热阻与电路板的整体厚度成正比,导热孔也是影响热阻值的因素之一。因此,对于采用方形扁平式无引脚(QFN)封装的大功率GaN器件,通常选用厚度为8mil密尔(毫英寸)的超薄PCB,以最大程度降低热阻。PCB材料的热性能还受到铜在电路板上铺设方式的影响。

要将热量向下方安装散热片的区域传递,至少需要使用散热孔。散热孔是在电路板上钻出的镀铜孔,用于形成从一个铜层到下一个铜层的导热通道。铜层越厚越好,因为它提供了极佳的导热性,但使用的铜越多,成本也越高。

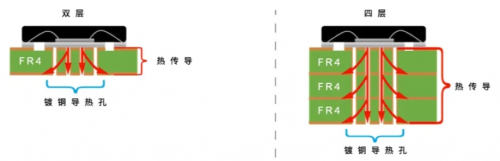

在低功率应用中,增加PCB的层数对元件的热传导具有显著影响。双层电路板和四层电路板之间的温差可能高达20°C,具体取决于铜平面的散热布局设计(如图2所示)。

图2,热传导性能——双层与四层PCB对比

尽管对于低功率场景,增加PCB层数能够带来一定的益处,但在高功率应用中却会产生适得其反的效果。例如,在诸如GaN高功率器件等应用中,特别是在功率超过10至15瓦的情况下,增加PCB层数不仅会增加热阻,还可能干扰热传导路径。

大功率GaN器件应用注意事项

针对GaN器件及单片微波集成电路(MMIC)进行热分析时,推荐采用一种综合方法;这种方法充分利用器件建模、经验测量(包括微型拉曼热成像)以及有限元分析(FEA)仿真,已被证明为最有效且最准确的手段。一旦完成基线热模型的建立,便可通过FEA来精准预测器件级的沟道温度及热阻。

如果无法使用微型拉曼热成像和FEA建模,而只能使用红外(IR)相机,那么必须清楚了解IR成像在精度上的局限。IR相机的空间分辨率比FET沟道的栅极长度大一个数量级,并且得到的表面温度为面积均值,远低于真实的最高沟道温度。

建议与GaN器件供应商的应用团队紧密合作,以确保GaN器件在您的应用中以足够低的温度运行。还可以从其应用团队获得产品整体散热模型,并将其纳入您的系统级散热模型中,以更准确地评估器件运行环境,进而确定由此产生的结温或沟道温度。

提高应用中的导热性

·仅针对裸片的应用

对于GaN裸片元件,应直接将其安装在导热性良好的散热片材料上或中间载板上,例如使用裸片贴片(die-on-tab)方式。安装时,应(优先)使用金锡共晶焊料或高导热性环氧树脂。散热片可以与下一级组件集成,也可使用焊料或导电环氧树脂以裸片贴片的结构直接安装在下一级组件的散热片上。

金锡焊料和许多导热性环氧树脂具有较低的热阻值,并且能够承受热膨胀系数(CTE)失配造成的应力(在将GaN芯片安装到高导热性材料上时经常出现)。确保金锡焊点无空隙非常重要,尤其是在裸片有效区域下方。如果采用导电的环氧树脂较薄的情况下,则银浆必须均匀、无空隙,以最大限度提高热导率。

不建议将GaN裸片功率器件直接安装在印刷电路板上,除非将其安装在高导热金属块(如铜块)上,以保证足够的热传导。

·GaN QFN和表面贴装封装应用

GaN QFN和表面贴装封装组件直接安装在PCB上。这些GaN放大器通常用于中等功率耗散的应用中;无论是连续波(CW)模式还是脉冲应用。在这些场景中,需要采用铜质导热通孔来为系统散热片提供导热路径。在选择通孔的尺寸、位置、类型以及镀铜量时,应充分考虑优化PCB设计的整体导热性能。

对于GaN QFN封装,建议将PCB厚度降至最低(如0.008英寸),以保持较低的热阻。使用具有密集通孔阵列的薄型PCB尤为重要,尤其对于高频GaN MMIC。

导热路径通常是器件散热的最有效途径。对于QFN和表面贴装封装放大器,确保从封装底部输出的面积均值CW热通量大于1W/mm²非常重要。此外,强烈建议使用镶埋铜块的PCB,以为系统散热片提供良好的导热路径。此外,对于任何热通量超过2 W/mm²的应用,都必须在封装下方镶埋铜块。

·GaN镀铜(CP)与法兰式封装应用

在大功率GaN封装晶体管或封装MMIC与散热片之间,具备良好的热界面非常关键。

封装连接不良是导致热失效的一个主要原因。在高功率情况下,Qorvo建议使用由导热材料(如铟片或石墨膜)制成、厚度为2到4mil密尔(约50-100µm)的热界面材料(TIM);或者,也可使用厚度为1到2mil密尔(约25-50µm)的导热膏或导热化合物,覆盖整个封装基底区域,以便安装法兰式封装的器件。

TIM的使用中有一个要点需要注意:为了获得良好的热传导效果,必须施加足够的压力。在采用导热膏或导热化合物时,应确保至少达到80%的覆盖率。

结论

良好的热设计对于现场可靠运行十分关键;特别是针对那些产生大量热量的大功率元件而言,重要性更不言而喻。

通过遵循基于最佳实践的热设计技术,工程师们能够确保系统性能的优化,最大限度地减少潜在问题,并尽可能地延长元件的使用寿命。

文章转载自Qorvo半导体微信公众号